以下這篇文章,是我今天翻網路找到的...提出順便把他轉貼過來,

也有提供連結,但怕改天連不到,所以還是再貼一次,有興趣可以連結到原始地方。

這是一種軟硬體之間的系統觀念...(您要稱為Firmware 也可以...)

當然啊...也有很多人在討論這種RTOS的東西 ...包括之前的難兄難弟:

http://GodspeedLee.myweb.hinet.net/

之前我們在搞那個FxxA就是有點類似的利用硬體的觀念來作分時多工...

但是呢?!...我們都知道現在的FPGA真的越來越強大了,速度也越來越快!...

(至少全世界的Fabless IC設計公司的前五大裡,就有兩家是作FPGA的!)

所以啦...現在FPGA 都開始可以讓您直接塞一棵8051進來(還有ARM7呢!)...。

而現在呢?!既然塞8051進來,乾脆也一部份的韌體也包進來算了 。

我前兩天不是提到MCU所謂的下Mask Code的作法嗎?!...為何不能直接用FPGA的方式呢?!

貼這篇文章的原因,最主要的原因還是底下的那張圖啊。

我們原本在MCU寫的韌體程式,無非也是希望他是成為硬體控制的一部份。

而既然有如此的觀念,人家就直接用FPGA 作了....

-----

當然啊...這裡還要提一個很好玩的事...(但應該不好笑吧!)

以前我們都覺得IC設計是一件多麼遠不可及的事...好像開IC是一件很偉大的事...

結果呢?這幾年下來,是不是每一家IC設計都是那麼賺錢?!我是不知道。

我確定的是:現在滿街會寫FPGA的人鐵定不少....以前啊...一家所謂系統廠商啊..

都是傻傻的等人家IC設計公司會提供怎樣的解決方案給他們開發產品。或是啊...

那怕自己在某一個系統應用領域裡,已經成熟為佼佼者時,往往為了要跟上游的IC設計合作,

就不得不開出自己的系統需求規格(其實就是一些Know-how...),

結果都讓這些IC設計公司反而到處賣解決方法給自己競爭對手...真是"養老鼠咬布袋"!

後果就是市場一片殺價競爭...大家都是過苦日子...

但是現在呢?!...FPGA 功能越來越強...支持的執行速度越來越快...

還有啊...滿街會寫FPGA的...或是昔日IC設計公司的設計大將轉戰應用市場...

現在一些比較大的系統廠商都已經可以掌握FPGA開發能力 ,甚至也熟知整個IC設計生產流程...

因為在這個大環境裡,開IC也不是什麼偉大或是困難的事情。(人家還怕您不開IC呢!)

所以啊...乾脆自己搞FPGA的IC設計...等一切穩定了,...自己想把他轉成Gate-Level,

在往IC上游一丟...既又可以保護自己的智慧財產,有可以保有自己的競爭力....

至少...那些純搞IC設計公司就不會拿出去到處灑解決方案...破壞市場價格!一舉多得啊!

------

當然您會說:FPGA 怎麼作成本也比較高啊...但是保護自己的 Know-how就是保障價格與毛利啊!

自己開IC哪有那麼容易啊?!...對啊...但您也不要忘記...

以前那些EDA Tools都非得要工作站級的電腦啊..

但現在的EDA tools啊...可能比會寫FPGA的人還多很多耶....(因為很多提供給學校裡的到處都是!)

我想我這樣的想法沒有不可的地方啊...有些大型應用系統原本本來就是全靠FPGA來設計的啦...

只不過,這一兩年來FPGA的價格也越來越平價化...(當然啊...那種上千腳的FPGA也不便宜啊!)

所以啊...我是覺得這是一種市場與系統應用的趨勢...不是每一種產品都非得開IC來作的...

(現在很多IC設計公司的人啊...天天嘛都跟別人問說...您這個產品我可以幫您開IC喔...

或是,動不動都想用開IC的方式來作產品或看市場...為開IC而開IC搞市場...

這種開公司、作產品的動機不是很健康....尤其在這種高度同性質競爭的環境...)

而也不是每一種應用都可以純粹用現有的解決方案可以作的...

在介於這兩者之間...這也不失一種適合的解決方法.....反正啊。

這種市場總是有人每天在想的啦...至於,每個人最後想到的方法是一樣的?!

就不得而知了...或許您會有您自己的想法也不一定,也未必同意我的看法!

但我只知道...如果還固守既有想法,卻還走不出一條路時,就得要另闢生路啊!

----------------------------------------------

http://www.actel.com/products/mpu/firmware/default.aspx

Processor Firmware

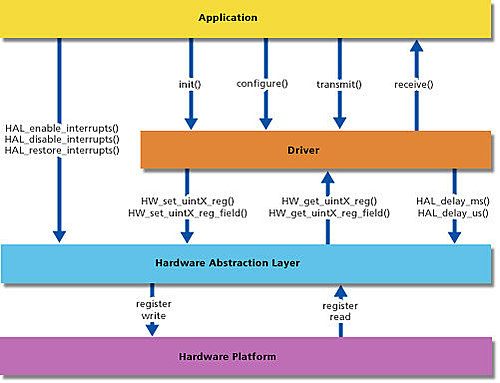

The firmware in a design using a processor in an Actel FPGA is organized into layers. The bottom layer consists of the processor, peripheral IP cores, and the FPGA device (collectively called the hardware platform). The hardware platform is highly configurable due to the flexibility of FPGA-based designs and can be based around one or more processors and any number of IP cores. The hardware platform operating frequency is also variable. At the top layer of the firmware is the application layer, which is the user's application domain. Ideally, the application layer should be completely isolated from variations in the hardware platform. Variations in processor type or operating frequency should be transparent to the application layer. Isolation between the hardware platform and the application layer is achieved through the use of two additional layers: the hardware abstraction layer (HAL) and the software drivers.

(Bare Metal Firmware Architecture)

Software Drivers

Actel has a range of processors and subsystem IP available for use in building system-level designs in our FPGA devices. Actel has developed software drivers to ease the use of the subsystem cores with the Cortex™-M1, CoreMP7 (ARM7), and Core8051s processors. The drivers are available for FREE and delivered as C source, so that they can be easily edited, if needed, and included in a program file. The drivers provide a set of functions used to make use of the subsystem peripherals. These drivers hide the implementation details of a peripheral's operations behind a driver application programming interface (API). This allows the application developer to be only concerned with a peripheral's function and not its internal operation.

Software drivers are available for the following cores and can be individually downloaded by clicking on the links below:

You can also download all of the drivers in a bundle.

The HALs enable the software drivers to be used without modification with Cortex-M1, CoreMP7 and Core8051s and are available for FREE. The software driver's interaction with the hardware platform is done through the HAL. This isolates the driver's implementation from the hardware platform variations. A driver implementation typically interacts with the hardware peripheral it is controlling through sequences of register reads and register writes. The implementation of the HAL translates the read and write requests into the bus transactions relevant to the hardware platform. This enables programmers to seamlessly reuse code even when the hardware platform changes.

The Cortex-M1 HAL is included with each individual software driver that is available for download.

Using a Real-Time Operating System (RTOS) adds two layers to the basic bare metal architecture described above. The application is written using the RTOS API. An RTOS adaptation layer is used to interface the Actel HAL and bare metal drivers to the RTOS driver framework.

(RTOS-based System Firmware Architecture)

The software drivers and HALs can be used in systems that use the following RTOS:

- Bare Metal (no RTOS)

- Micrium µC/OS-II

沒有留言:

張貼留言